日本特許7206472号 オンキョーの特許。

庁から公開されている請求項

(57)【特許請求の範囲】

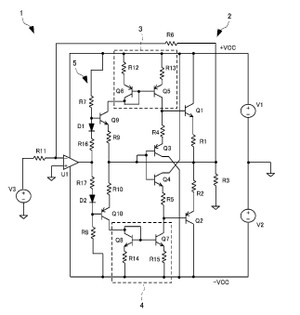

【請求項1】

入力される信号を増幅するプッシュプル回路と、

前記プッシュプル回路により増幅された信号が入力され、出力端子に前記プッシュプル回路の出力端子が接続されたダイヤモンドバッファ回路と、

電源と前記ダイヤモンドバッファ回路とに接続され、前記プッシュプル回路の引き込み電流端子に接続されたカレントミラー回路と、

を備えることを特徴とする増幅装置。

【請求項2】

前記カレントミラー回路は、

正側の電源と前記ダイヤモンドバッファ回路とに接続され、前記プッシュプル回路の正側の引き込み電流端子に接続された第1カレントミラー回路と、

負側の電源と前記ダイヤモンドバッファ回路とに接続され、前記プッシュプル回路の負側の引き込み電流端子に接続された第2カレントミラー回路と、を有することを特徴とする請求項1に記載の増幅装置。

【請求項3】

前記ダイヤモンドバッファ回路は、

コレクタが、正側の電源に接続され、

エミッタが、第1抵抗を介して、負荷に接続され、

ベースが、第4抵抗を介して、第3バイポーラトランジスタのエミッタに接続された、npn型の第1バイポーラトランジスタと、

コレクタが、負側の電源に接続され、

エミッタが、第2抵抗を介して、前記負荷に接続され、

ベースが、第5抵抗を介して、第4バイポーラトランジスタのエミッタに接続された、pnp型の第2バイポーラトランジスタと、

コレクタが、負側の電源に接続され、

エミッタが、前記第4抵抗を介して、前記第1バイポーラトランジスタのベースと、前記第1カレントミラー回路と、に接続され、

ベースが、前記プッシュプル回路の出力に接続された、pnp型の前記第3バイポーラトランジスタと、

コレクタが、正側の電源に接続され、

エミッタが、前記第5抵抗を介して、前記第2バイポーラトランジスタのベースと、前記第2カレントミラー回路と、に接続され、

ベースが、前記プッシュプル回路の出力に接続された、npn型の前記第4バイポーラトランジスタと、を有し、

出力端子は、前記第1抵抗と前記第2抵抗との接続点であることを特徴とする請求項2に記載の増幅装置。

【請求項4】

前記第1カレントミラー回路は、

コレクタが、前記ダイヤモンドバッファ回路に接続され、

エミッタが、第13抵抗を介して、正側の電源に接続され、

ベースが、第6バイポーラトランジスタのベースとコレクタとに接続された、pnp型の第5バイポーラトランジスタと、

コレクタが、ベースと、前記プッシュプル回路の正側の引き込み電流端子と、前記第5

バイポーラトランジスタのベースと、に接続され、

エミッタが、第12抵抗を介して、正側の電源に接続され、

ベースが、コレクタと、前記第5バイポーラトランジスタのベースと、に接続された、pnp型の前記第6バイポーラトランジスタと、を有し、

前記第2カレントミラー回路は、

コレクタが、前記ダイヤモンドバッファ回路に接続され、

エミッタが、第15抵抗を介して、負側の電源に接続され、

ベースが、第8バイポーラトランジスタのベースとコレクタとに接続された、npn型の第7バイポーラトランジスタと、

コレクタが、ベースと、前記プッシュプル回路の負側の引き込み電流端子と、前記第7バイポーラトランジスタのベースと、に接続され、

エミッタが、第14抵抗を介して、負側の電源に接続され、

ベースが、コレクタと、前記第7バイポーラトランジスタのベースと、に接続された、npn型の前記第8バイポーラトランジスタと、を有することを特徴とする請求項2又は3に記載の増幅装置。

【請求項5】

前記プッシュプル回路は、

ベースが、第7抵抗と第1ダイオードとの間に接続され、

コレクタが、前記第1カレントミラー回路に接続された、正側の引き込み電流端子であり、

エミッタが、第9抵抗を介して、前記ダイヤモンドバッファ回路の入力に接続された、npn型の第9バイポーラトランジスタと、

ベースが、第8抵抗と第2ダイオードとの間に接続され、

コレクタが、前記第2カレントミラー回路に接続された、負側の引き込み電流端子であり、

エミッタが、第10抵抗を介して、前記ダイヤモンドバッファ回路の入力に接続された、pnp型の第10バイポーラトランジスタと、

前記第1ダイオードと入力との間に接続された第16抵抗と、

前記第2ダイオードと入力との間に接続された第17抵抗と、

を有し、

出力端子は、前記第9抵抗と前記第10抵抗との接続点であることを特徴とする請求項2~4のいずれか1項に記載の増幅装置。

【請求項6】

入力される信号を増幅するオペアンプをさらに備え、

前記オペアンプの負側の入力端子に、第11抵抗を介して、信号が入力され、

前記オペアンプの正側の入力端子が、基準電位に接続され、

前記オペアンプの出力端子が、前記プッシュプル回路の入力に接続され、

負荷と前記オペアンプの負側の入力端子との間に第6抵抗が接続されていることを特徴とする請求項1~5のいずれか1項に記載の増幅装置。

よく見かける回路のように思えるが、何が特徴なのか?

カレントミラー 3 と 4 を入れたのが進歩性で申請が通ったようだが、 どこかで見た記憶はあるね。 「外部でNFB」も1970年代技術。

ICメーカーはこんな古典手法(1980年代技術)は争わないので、ICメーカ公開の等価回路に見つけらえそうな案件。

出願日】平成30年5月7日(2018.5.7)

【審査請求日】令和3年5月1日(2021.5.1)

権利侵害との連絡がない?? ので、請求期限まぎわで請求をかけたら、認定された と読み取れる。

スンゴイ特許でなく A+B+C+Dにしたら 新特許として認められた例のひとつだね。ただ信号を扱う半導体数が増えるので、いくらでも色つけできるのは避けられない。

この特許に疑義があるようであれば不服請求?を掛けることもできる。 SEPP起因の波形非対称は避けてとおれないのも事実。

コメント